Versio n: 2.0

### TECHNICAL SPECIFICATION

MODEL NO.: ED097OC1

The content of this information is subject to be changed without notice. Please contact PVI or its agent for further information

| Customer•s Confirmation |

|-------------------------|

|                         |

| Customer                |

|                         |

|                         |

| Date                    |

|                         |

| Ву                      |

#### FOR MORE INFORMATION:

AZ DISPLAYS, INC. 75 COLUMBIA, ALISO VIEJO, CA, 92656 Http://www.AZDISPLAYS.com

Confirmed By

Prepared By

Revision History

| Rev. | Issued Date     | Revised                                                            | Contents                                                                                                                                                                                                   |

|------|-----------------|--------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.0  | Set.10.2008     | New                                                                |                                                                                                                                                                                                            |

| 2.0  | November.7.2008 | Add<br>Page 7<br>Page 12<br>Modify<br>Page 4<br>Page 10<br>Page 12 | 6-2) Absolute maximum rating Note 8-1  3. Mechanical Specifications 7. Power on Sequence 8-1)Specifications Add Contrast ratio Typ= 7 Update time 1000/540 change to 780/260 ( 2-4 bits/1bits) 14. Packing |

# TECHNICAL SPECIFICATION CONTENTS

| NO. | ITEM                                          | PAGE |

|-----|-----------------------------------------------|------|

| -   | Cover                                         | 1    |

| _   | Revision History                              | 2    |

| -   | Contents                                      | 3    |

| 1   | Application                                   | 4    |

| 2   | Features                                      | 4    |

| 3   | Mechanical Specifications                     | 4    |

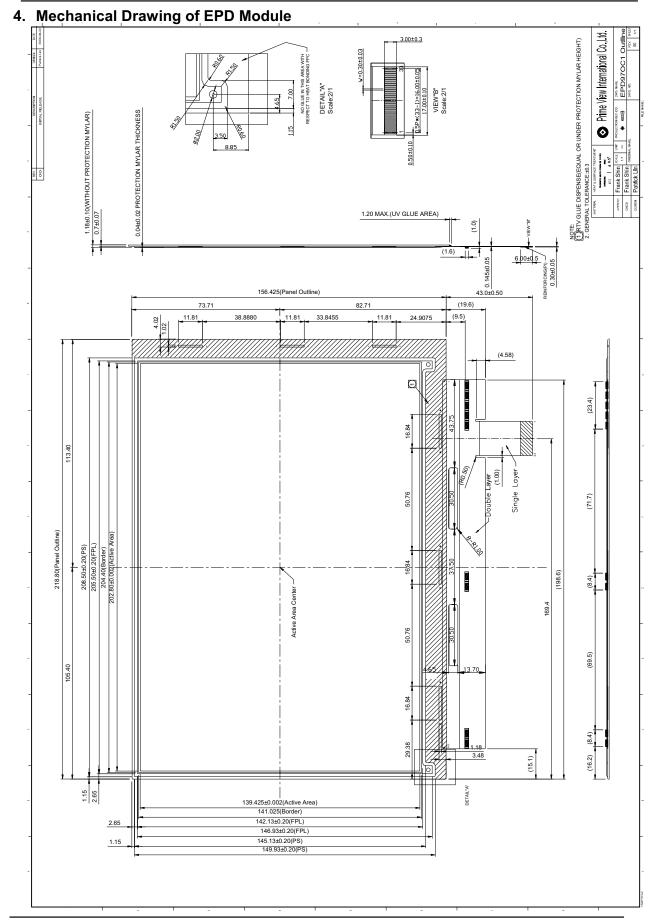

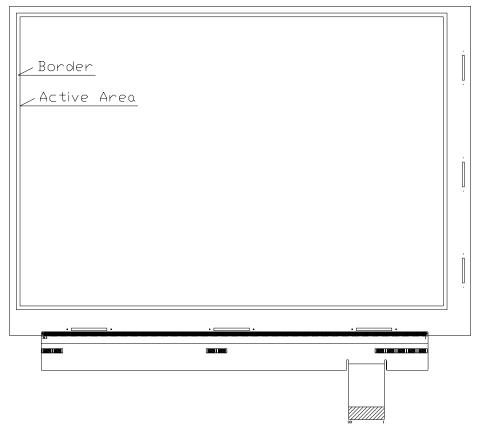

| 4   | Mechanical Drawing of EPD module              | 5    |

| 5   | Input/Output Terminals                        | 6    |

| 6   | Electrical Characteristics                    | 7    |

| 7   | Power on Sequence                             | 10   |

| 8   | Optical Characteristics                       | 12   |

| 9   | Handling, Safety and Environment Requirements | 14   |

| 10  | Reliability test                              | 15   |

| 11  | Bar Code definition                           | 16   |

| 12  | Border definition                             | 17   |

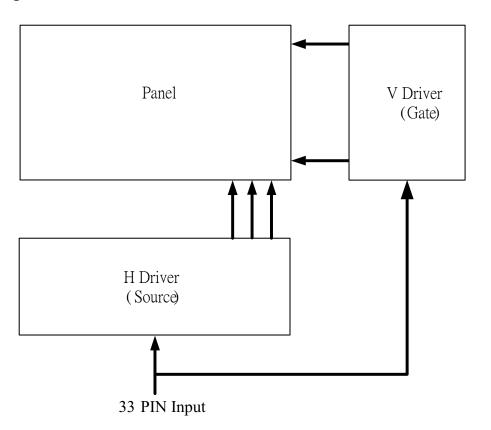

| 13  | Block Diagram                                 | 17   |

| 14  | Packing                                       | 18   |

#### 1. Application

The display is a TFT active matrix electrophoretic display, with associated interface and control logic, and a reference system design.

The 9.7" active area contains 1200x825 pixels, and has full 1~4 bit display capabilities An integrated circuit containing interface, timing and control logic is supplied with each panel.

#### 2. Features

- High contrast TFT electrophoretic

- > 1200x825 display

- > High reflectance

- Ultra wide viewing angle

- > Ultra low power consumption

- > Pure reflective mode

- ➢ Bi-stable

- Commercial temperature range

- Landscape, portrait mode

- Antiglare hard-coated front-surface

#### 3. Mechanical Specifications

| Parameter           | Specifications              | Unit  | Remark |

|---------------------|-----------------------------|-------|--------|

| Screen Size         | 9.7                         | Inch  |        |

| Display Resolution  | 1200 (H) ×825(V)            | Pixel |        |

| Active Area         | 202.8 (H)×139.425 (V)       | mm    |        |

| Pixel Pitch         | 0.169(H)x0.169(V)           | mm    |        |

| Pixel Configuration | Rectangle                   |       |        |

| Outline Dimension   | 218.8(H)×156.425(V)×1.18(D) | mm    |        |

| Module Weight       | 80±5                        | g     |        |

## 5.Input/Ouput Terminals 5-1)Pinout List

| Pin# | Signal | Description                         |

|------|--------|-------------------------------------|

| 1    | VNEG   | Negative power supply source driver |

| 2    | NC     | NO Connection                       |

| 3    | VPOS   | Positive power supply source driver |

| 4    | NC     | NO Connection                       |

| 5    | VSS    | Ground                              |

| 6    | NC     | NO Connection                       |

| 7    | VDD    | Digital power supply drivers        |

| 8    | XCL    | Clock source driver                 |

| 9    | XLE    | Latch enable source driver          |

| 10   | XOE    | Output enable source driver         |

| 11   | XSHR   | Shift direction source driver       |

| 12   | XSTL2  | Start pulse source driver           |

| 13   | D0     | Data signal source driver           |

| 14   | D1     | Data signal source driver           |

| 15   | D2     | Data signal source driver           |

| 16   | D3     | Data signal source driver           |

| 17   | D4     | Data signal source driver           |

| 18   | D5     | Data signal source driver           |

| 19   | D6     | Data signal source driver           |

| 20   | D7     | Data signal source driver           |

| 21   | NC     | NO Connection                       |

| 22   | VCOM   | Common connection                   |

| 23   | NC     | NO Connection                       |

| 24   | VGG    | Positive power supply gate driver   |

| 25   | NC     | NO Connection                       |

| 26   | VEE    | Negative power supply gate driver   |

| 27   | NC     | NO Connection                       |

| 28   | MODE2  | Output mode selection gate driver   |

| 29   | MODE1  | Output mode selection gate driver   |

| 30   | XRL    | Shift direction gate driver         |

| 31   | SPV    | Start pulse gate driver             |

| 32   | CKV    | Clock gate driver                   |

| 33   | BORDER | Border connection                   |

#### **6.Electrical Characteristics**

#### 6-1) Panel interface description

This panel is intended to be driven by EPD display controller ASIC.

#### 6-2) Absolute maximum rating

| Parameter                | Symbol                              | Rating        | Unit                   |

|--------------------------|-------------------------------------|---------------|------------------------|

| Logic Supply Voltage     | VDD                                 | -0.3 to +7    | V                      |

| Positive Supply Voltage  | $V_{POS}$                           | -0.3 to +18   | V                      |

| Negative Supply Voltage  | $V_{NEG}$                           | +0.3 to -18   | V                      |

| Max .Drive Voltage Range | V <sub>POS</sub> - V <sub>NEG</sub> | 36            | V                      |

| Supply Voltage           | VGG                                 | -0.3 to +45   | V                      |

| Supply Voltage           | VEE                                 | -25.0 to +0.3 | V                      |

| Supply Range             | VGG-VEE                             | -0.3 to +45   | V                      |

| Operating Temp. Range    | TOTR                                | 0 to +50      | $^{\circ}\!\mathbb{C}$ |

| Storage Temperature      | TSTG                                | -25 to +70    | $^{\circ}\!\mathbb{C}$ |

#### 6-3) Panel DC characteristics

| Parameter                                                          | Symbol                | Conditions                         | Min   | Тур      | Max   | Unit                   |

|--------------------------------------------------------------------|-----------------------|------------------------------------|-------|----------|-------|------------------------|

| Signal ground                                                      | $V_{SS}$              |                                    | -     | 0        | -     | V                      |

| Legie Veltege europh                                               | $V_{\text{DD}}$       |                                    | 3.0   | 3.3      | 3.6   | V                      |

| Logic Voltage supply                                               | $I_{VDD}$             | V <sub>DD</sub> =3.3V              | -     | 0.75     | 1.5   | mA                     |

| Cata Nagativa ayanlı                                               | $V_{EE}$              |                                    | -21   | -20      | -19   | V                      |

| Gate Negative supply                                               | I <sub>EE</sub>       | GV <sub>EE</sub> =-20V             | _     | 3.9      | 11.7  | mA                     |

| Cata Positivo supply                                               | $V_{GG}$              |                                    | 21    | 22       | 23    | V                      |

| Gate Positive supply                                               | $I_{GG}$              | GV <sub>DD</sub> = 22V             | _     | 3.3      | 9.9   | mA                     |

| Course Negative europy                                             | $V_{NEG}$             |                                    | -15.4 | -15      | -14.6 | V                      |

| Source Negative supply                                             | $I_{NEG}$             | V <sub>NEG</sub> = -15V            | -     | 44.9     | 89.8  | mA                     |

| Source Positive supply                                             | $V_{POS}$             |                                    | 14.6  | 15       | 15.4  | V                      |

| Source Positive supply                                             | $I_{POS}$             | V <sub>POS</sub> = 15V             | -     | 44.1     | 88.3  | mA                     |

| Pordor oupply                                                      | 17                    | V <sub>POS</sub> = 15V             | 14.6  | 15       | 15.4  | V                      |

| Border supply                                                      | $V_{\mathrm{Border}}$ | V <sub>NEG</sub> = -15V            | -15.4 | -15      | -14.6 | V                      |

| Asymmetry source                                                   | $V_{Asym}$            | V <sub>POS</sub> +V <sub>NEG</sub> | -800  | 0        | 800   | mV                     |

| Common voltage                                                     | $V_{\text{COM}}$      |                                    | -2    | Adjusted | -0.3  | V                      |

| Common voitage                                                     | I <sub>COM</sub>      |                                    | -     | 0.59     | -     | mA                     |

| Maximum power panel                                                | $P_{MAX}$             |                                    | -     | -        | 3200  | mW                     |

| Standby power panel                                                | $P_{STBY}$            |                                    | -     | -        | 0.6   | mW                     |

| Typical power panel                                                | $P_{TYP}$             |                                    | -     | 1500     | -     | mW                     |

| Operating temperature                                              |                       |                                    | 0     | -        | 50    | $^{\circ}\!\mathbb{C}$ |

| Storage temperature                                                |                       |                                    | -25   | -        | 70    | $^{\circ}\!\mathbb{C}$ |

| Maximum image update time at 25 $\!\!\!\!\!\!\!\!^{\circ}_{\circ}$ |                       |                                    | -     | 1000     | -     | ms                     |

- The maximum power and maximum currents are specified for the worse case power consumption.

This occurs when 2 horizontal inverted stripped images are displayed

- The typical power is the consumed power when "typical images" are displayed.

- The standby power is the consumed power when the panel controller is in standby mode.

- The listed electrical/optical characteristics are only guaranteed under the controller & waveform provided by PVI

- Vcom is recommended to be set in the range of assigned value  $\pm 0.1 \text{V}$

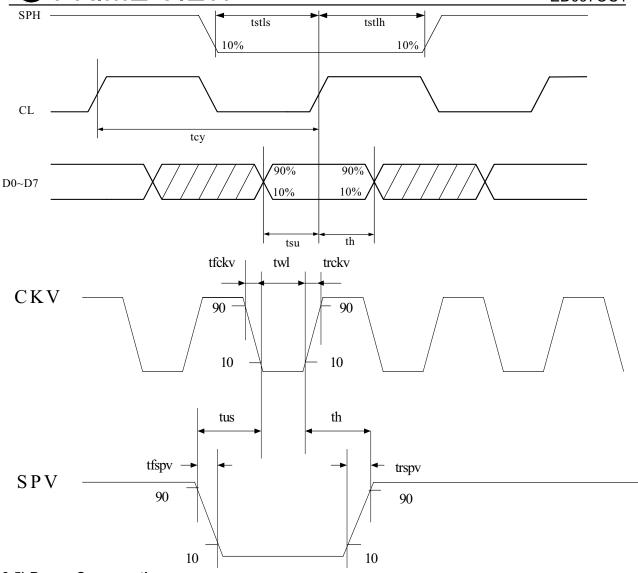

#### 6-4 )Panel AC characteristics

VDD=3.0V to 3.6V, unless otherwise specified.

| Parameter                     | Symbol | Min. | Тур. | Max. | Unit | App Pin |

|-------------------------------|--------|------|------|------|------|---------|

| Clock frequency               | fckv   | -    | -    | 200  | kHz  |         |

| Minimum "L" clock pulse width | twL    | 0.5  | -    | -    | us   | CKV     |

| Clock rise time               | trckv  | -    | -    | 100  | ns   |         |

| Clock fall time               | tfckv  | -    | -    | 100  | ns   |         |

| Data setup time               | tSU    | 100  | -    | -    | ns   | CKV,    |

| Data hold time                | tH     | 100  | -    | -    | ns   | SPV     |

| Pulse rise time               | trspv  | -    | -    | 100  | ns   | - OD) / |

| Pulse fall time               | tfspv  | -    | -    | 100  | ns   | SPV     |

| Clock CL cycle time           | tcy    | 50   | -    | DC   | ns   |         |

| D0 D7, SPH setup time         | tsu    | 8    | -    | -    | ns   |         |

| D0 D7, SPH hold time          | th     | 1    | -    | -    | ns   | Below   |

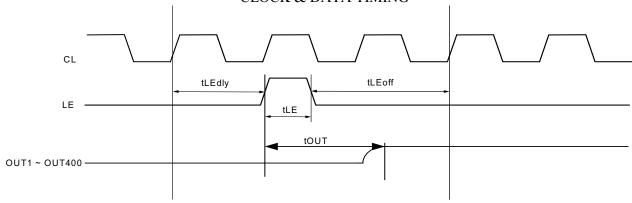

| LE on delay time              | tLEdly | 40   | -    | -    | ns   | table   |

| LE high-level pulse width     | tLEw   | 40   | -    | -    | ns   |         |

| LE off delay time             | tLEoff | 40   | _    | -    | ns   |         |

#### **CLOCK & DATA TIMING**

**OUTPUT LATCH CONTROL SIGNALS**

ED097OC1

#### 6-5) Power Consumption

| Parameter                                      | Symbol | Conditions | TYP  | Max  | Unit | Remark |

|------------------------------------------------|--------|------------|------|------|------|--------|

| Maximum panel power consumption during update. | ı      | -          | -    | 3200 | mW   |        |

| Power consumption in standby mode              | -      | -          | -    | 0.6  | mW   |        |

| Typical panel power                            | -      | -          | 1500 | ı    | mW   |        |

ED097OC1

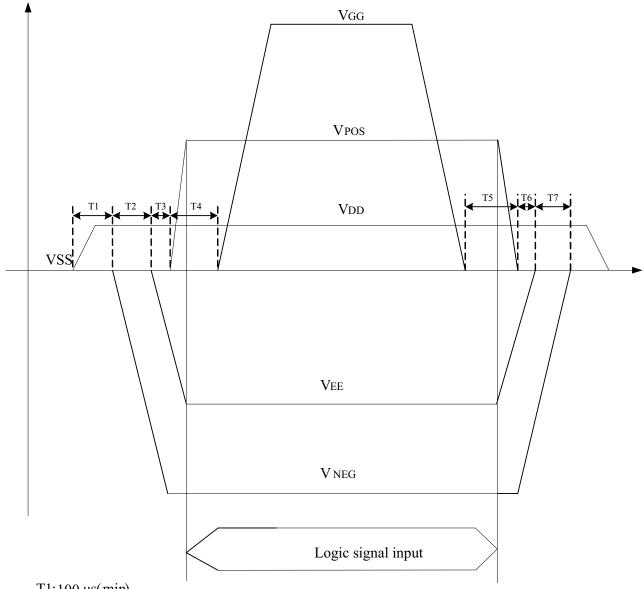

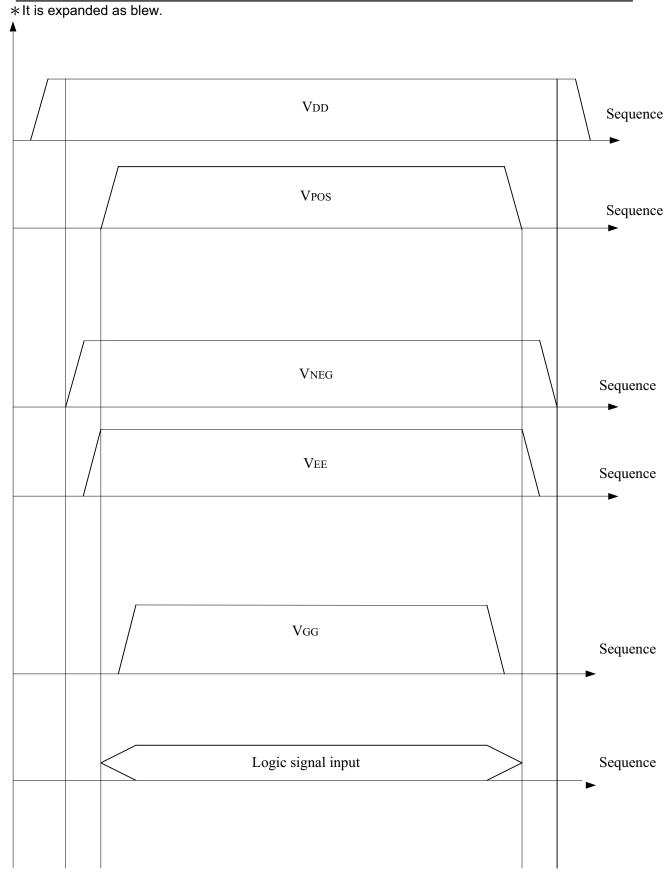

#### 7. Power on Sequence

- 1. VSS → VDD → VNEG → VPOS (Source driver)

- 2. VEE → VGG(Gate driver)

T1:100 µs(min)

T2: 0µs(min)

T3:  $1000 \mu s (min)$

T4: 0 µs (min)

T5: 0 μs (min)

$T6:0 \mu s (min)$

T7: 0 \( \text{is (min)} \)

#### 8. Optical characteristics

#### 8-1)Specifications

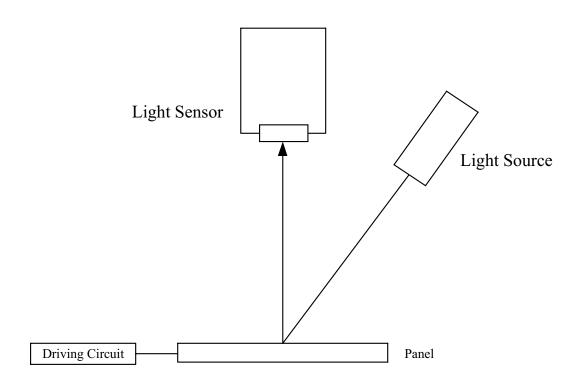

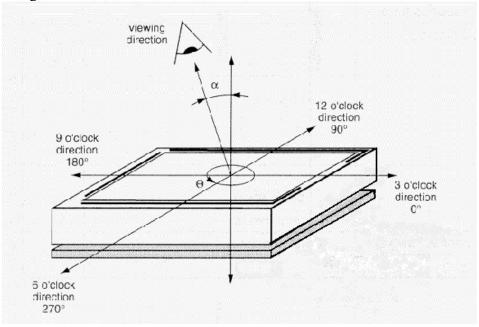

Measurements are made with that the illumination is under an angle of 30 degrees, the detection is perpendicular unless otherwise specified.

| _ | Г | = | 2 | 5 | 0 | ( |

|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |

| SYMBOL              | PARAMETER                  | CONDITIONS                 | MIN | TYP.               | MAX | UNIT     | Note     |

|---------------------|----------------------------|----------------------------|-----|--------------------|-----|----------|----------|

| R                   | Reflectance                | White                      | 30  | 35                 | -   | %        | Note 8-1 |

| Gn                  | N <sub>th</sub> Grey Level | -                          | -   | DS+(WS-DS)xn/(m-1) | ı   | L*       | -        |

| CR                  | Contrast Ratio             | -                          | 6   | 7                  | 1   |          | -        |

| T <sub>update</sub> | Update time                | 2~4-bit mode<br>1-bit mode |     | 780<br>260         | ı   | ms<br>ms | -        |

WS: White state , DS: Dark state, Gray state from Dark to White :DS  $\cdot$  G1  $\cdot$  G2...  $\cdot$  Gn...  $\cdot$  Gm-2  $\cdot$  WS m:4  $\cdot$  8  $\cdot$  16 when 2  $\cdot$  3  $\cdot$  4 bits mode

Note 8-1: Luminance meter :Eye – One Pro Spectrophotometer

#### 8-2) Definition of contrast ratio

The contrast ratio (CR) is the ratio between the reflectance in a full white area (Rl) and the reflectance in a dark area (Rd):

CR = R1/Rd

#### 8-3)Reflection Ratio

The reflection ratio is expressed as:

$R = Reflectance \ Factor_{white \ board} \quad x \quad \left( \ L_{center} \ / \ L_{white \ board} \ \right)$

$L_{center}$  is the luminance measured at center in a white area (R=G=B=1).  $L_{white \, board}$  is the luminance of a standard white board. Both are measured with equivalent illumination source. The viewing angle shall be no more than 2 degrees.

#### 9. HANDLING, SAFETY AND ENVIROMENTAL REQUIREMENTS

#### **WARNING**

The display glass may break when it is dropped or bumped on a hard surface. Handle with care. Should the display break, do not touch the electrophoretic material. In case of contact with electrophoretic material, wash with water and soap.

#### **CAUTION**

The display module should not be exposed to harmful gases, such as acid and alkali gases, which corrode electronic components.

Disassembling the display module can cause permanent damage and invalidate the warranty agreements.

Observe general precautions that are common to handling delicate electronic components. The glass can break and front surfaces can easily be damaged. Moreover the display is sensitive to static electricity and other rough environmental conditions.

| Data sheet status |                                                        |

|-------------------|--------------------------------------------------------|

| Product           | This data sheet contains final product specifications. |

| specification     |                                                        |

|                   |                                                        |

#### **Limiting values**

Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

#### **Application information**

Where application information is given, it is advisory and does not form part of the specification.

10. Reliability test

|    | TEST                                         | CONDITION                                                                                                    | METHOD                      | REMARK                                                                                             |

|----|----------------------------------------------|--------------------------------------------------------------------------------------------------------------|-----------------------------|----------------------------------------------------------------------------------------------------|

| 1  | High-Temperature<br>Operation                | T = +50°C, RH = 30% for 240 hrs                                                                              | IEC 60 068-2-2Bp            | At the end of the test, electric, mechanical, and optical specifications shall be satisfied.       |

| 2  | Low-Temperature<br>Operation                 | T = 0°C for 240 hrs                                                                                          | IEC 60 068-2-2Ab            | At the end of the test, electric, mechanical, and optical specifications shall be satisfied.       |

| 3  | High-Temperature<br>Storage                  | T = +70°C, RH=23% for 240 hrs                                                                                | IEC 60 068-2-2Bp            | At the end of the test, electric, mechanical, and optical specifications shall be satisfied.       |

| 4  | Low-Temperature<br>Storage                   | T = -25°C for 240 hrs                                                                                        | IEC 60 068-2-1Ab            | At the end of the test, electric,<br>mechanical, and optical specifications<br>shall be satisfied. |

| 5  | High-Temperature,<br>High-Humidity Operation | T = +40°C, RH = 90% for 168 hrs                                                                              | IEC 60<br>068-2-3CA         | At the end of the test, electric, mechanical, specifications shall be satisfied.                   |

| 6  | High Temperature,<br>High- Humidity Storage  | T = +60°C, RH=80% for 240hrs                                                                                 | IEC 60<br>068-2-3CA         | At the end of the test, electric, mechanical, specifications shall be satisfied.                   |

| 7  | Temperature Cycle                            | -25°C →+70°C, 100 Cycles<br>30min 30min                                                                      | IEC 60 068-2-14             | At the end of the test, electric, mechanical, specifications shall be satisfied.                   |

| 8  | UV exposure Resistance                       | 765 W/m² for 168hrs,40℃                                                                                      | IEC60 068-2-5Sa             | Optical characteristics shall be satisfied.                                                        |

| 9  | Package Vibration                            | 1.04G, Frequency: 10~500Hz<br>Direction: X,Y,Z<br>Duration: 1 hours in each direction                        | Full packed for shipment    | At the end of the test, electric, mechanical, and optical specifications shall be satisfied.       |

| 10 | Package Drop Impact                          | Drop from height of 122 cm on concrete surface. Drop sequence: 1 corner, 3 edges, 6 faces One drop for each. | full packed for<br>shipment | At the end of the test, electric, mechanical, and optical specifications shall be satisfied.       |

| 11 | Electrostatic Effect<br>(non-operating)      | (Machine model)+/- 250V<br>0Ω, 200pF                                                                         | IEC 62179, IEC 62180        | At the end of the test, electric, mechanical, specifications shall be satisfied.                   |

| 12 | Altitude test<br>Operation                   | 700hPa ( = 3000m )<br>48Hr                                                                                   |                             | At the end of the test, electric, mechanical, specifications shall be satisfied.                   |

| 13 | Altitude test<br>Storage                     | 260hPa(= 10000m)<br>48Hr                                                                                     |                             | At the end of the test, electric, mechanical, specifications shall be satisfied.                   |

| 14 | Stylus Tapping                               | POLYACETAL Pen: Top R:0.8mm<br>Load: 300gf<br>Speed: 2 times/sec<br>Total 13,500times,                       |                             | Pass criteria – no glass breakage or damage to microcapsules.                                      |

Actual EMC level to be measured on customer application

#### 11. Bar Code definition

<u>EOD</u> <u>00</u> <u>4</u> <u>01</u> <u>1</u> <u>I</u> <u>7</u> <u>4</u> <u>00361</u> <u>A</u> <u>T</u> <u>1</u> <u>2</u> <u>3</u> <u>4</u> <u>2</u> <u>5</u> <u>6</u> <u>2</u> <u>7</u> <u>2</u> <u>8</u>

1 : EPD model code:

ED097OC1:E0D

2 : Internal control codes:

3 : FPL reversion code

V100:3,V110:4

4 : FPL batch code:

(BL/P/B...)001~009:01~99, 100~109:A0~A9, 110-119:B0~B9... 320~329:Z0~Z9

5 : Year:

F:2005 / G:2006 / H:2007 / I:2008 /... / Z:2025

6 : Month:

1:Jan. 2:Feb. ... 9:Sep. A:Oct. B:Nov. C:Dec.

7 : Serial number

8 : MFG code:

TOC:T, PVI:P

ED097OC1

#### 12. Border definition

#### 13.Block Diagram

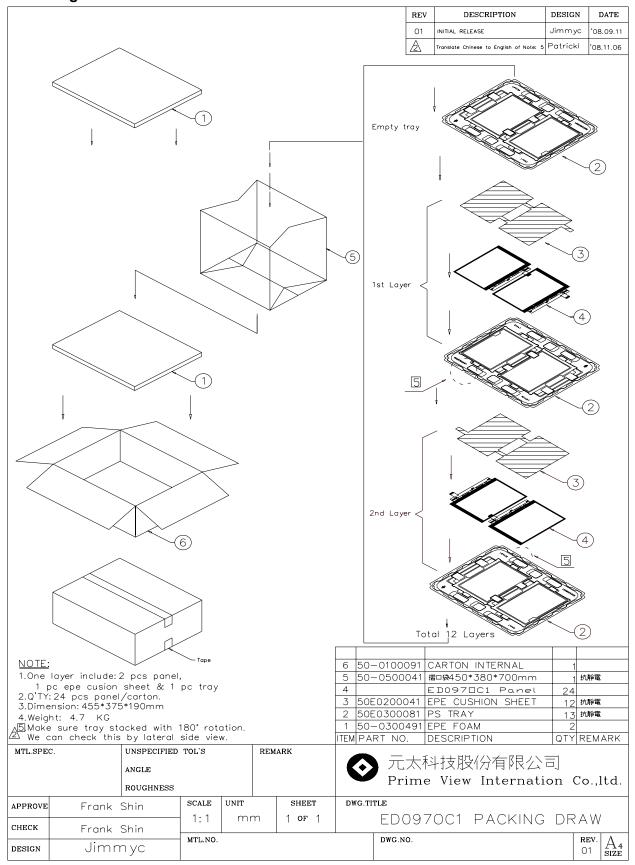

#### 14.Packing